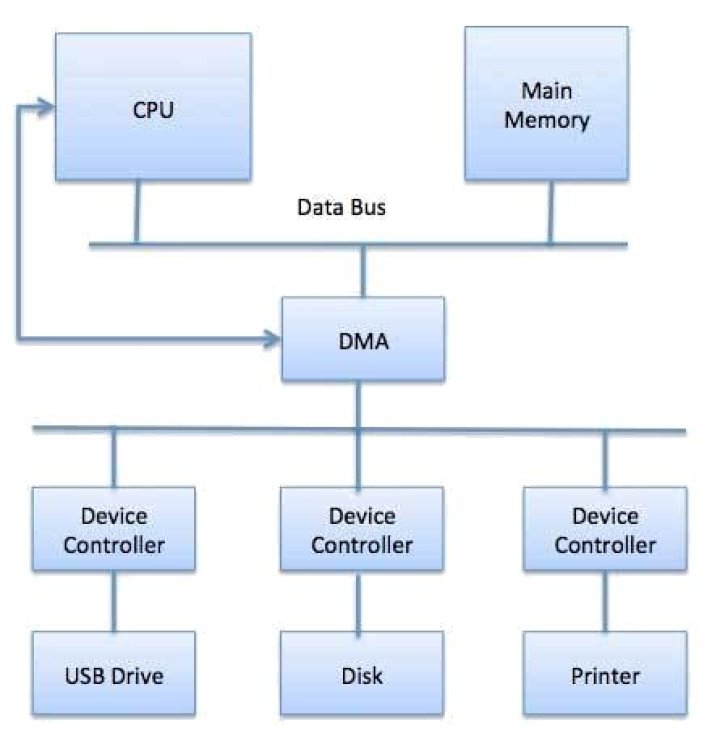

How does CPU/DMA access hard disk?

Considering x86 CPU / LINUX

I want to understand how does cpu or dma access the hard drive ?does hard drive have to be accessed through IO Port addresses or it has to mapped into the memory (MMIO) ?

1 Answer

The data on the hard drive is not part of physical address space.1 The data is not memory-mapped.

The SATA controller (for example) has I/O registers that the CPU needs to write to, to program it to make a DMA transfer of n sectors from a certain disk offset to a certain physical memory address.

Some or all of these I/O registers might be accessible via MMIO (normal loads and stores to special addresses) rather than in/out port IO. But it's still just a matter of sending the desired commands to the SATA controller. (For the details on that, see .) AHCI is the most widely used kind of kernel <-> hardware driver interface, but others exist (e.g. fancy RAID controllers that need their own drivers).

e.g. the AHCI SATA controller on my mobo, according to lspci -v:

00:17.0 SATA controller: Intel Corporation Q170/Q150/B150/H170/H110/Z170/CM236 Chipset SATA Controller [AHCI Mode] (rev 31) (prog-if 01 [AHCI 1.0]) Subsystem: ASUSTeK Computer Inc. Q170/Q150/B150/H170/H110/Z170/CM236 Chipset SATA Controller [AHCI Mode] Flags: bus master, 66MHz, medium devsel, latency 0, IRQ 135 Memory at f7248000 (32-bit, non-prefetchable) [size=8K] Memory at f724c000 (32-bit, non-prefetchable) [size=256] I/O ports at f090 [size=8] I/O ports at f080 [size=4] I/O ports at f060 [size=32] Memory at f724b000 (32-bit, non-prefetchable) [size=2K] Capabilities: <access denied> Kernel driver in use: ahci Kernel modules: ahciThose small two "memory" regions (2k and 8k) are almost certainly MMIO ports, but it does also have some I/O ports in I/O address space. The "non-prefetchable" is a hint there; if reads have a side effect, prefetch has to be disabled.

Note the flags: bus master. That means it can DMA to/from main memory.

But my NVMe SSD only has MMIO space, no legacy I/O ports.

03:00.0 Non-Volatile memory controller: Intel Corporation SSD 600P Series (rev 03) (prog-if 02 [NVM Express]) Subsystem: Intel Corporation SSD 600P Series Flags: bus master, fast devsel, latency 0, IRQ 16, NUMA node 0 Memory at f7000000 (64-bit, non-prefetchable) [size=16K] Capabilities: <access denied> Kernel driver in use: nvmeModern hard drive controllers don't make the CPU copy the data 4 or 8 bytes at a time with "programmed I/O". That was an option with classic IDE / ATA controllers, but only as a fallback in case something bad happened (like lockups or data corruption) on your motherboard or PCI HD controller when using hdparm to set the Linux drivers to use DMA transfers on pre-SATA systems.

Technically PIO is still an option for AHCI SATA controllers, apparently. But it's never the default; unlike in the bad old days when broken hardware was a real possibility, modern OSes can safely expect that DMA will work correctly.

Footnote 1: unless your "hard drive" is actually a non-volatile DIMM in a memory slot, like Intel Optane DC PM, or a battery-backed DRAM). Getting recently-stored data pushed from write-back CPU caches to non-volatile memory-mapped storage is one use-case for instructions like clflushopt or clwb.